在HDI板的设计中,导线特性阻抗一般均设定为50Ω。在SLC之前的FR4电路板特性阻抗约为800Ω。有时高密度FR4 HDI板的层数高达6层或8层,由于导线层距离接地层很远因此特性阻抗会增加到150Ω以上,而使得讯号杂讯大幅增加。后来由于CMOS晶片的功率较小因此在电路板的设计上才将特性阻抗降低为50Ω,为了降低讯号的杂讯,因此承载晶片的电路板特性阻抗一般也都是设定成50Ω。

为了减少线路所造成的杂讯问题,从以前的单晶片模组和多晶片模组等电路板模组都一直将特性阻抗为标准的50Ω,而主机板的封装杂导问题,如果能结合SLC和FCA技术,由于封装本身能达到高密度小型化,并将电路板特性阻抗与元件匹配设定为50Ω时,则可以大幅降低封装的杂讯问题。至于增层电路板,导体层厚度越薄杂讯的问题越小,不过如果要与目前FR4电路板的制程匹配的话,则以标准的18um导体层为主。

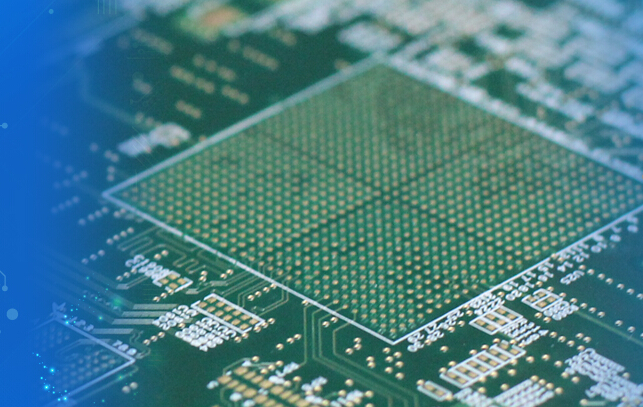

早期的增层电路板是在FR4电路板的基层上方利用增层法形成增层层。基层的主要功能除了作为基材支撑电路板的结构之外,在电路布局上通常也会将使用厚导体层的电源层配置在基层上以增加电路板的使用效率。而且增层层上的栓孔孔径较小,因此根据不同线路层的功能将基层和增层层中的线路分开也比较符合电路板的使用效率。

触摸屏HDI

触摸屏HDI 服务智能机器人线路板

服务智能机器人线路板 服务智能机器人线路板

服务智能机器人线路板 家庭智能机器人线路板

家庭智能机器人线路板